| RAM-COMM Expansion Board                  | 1 |

|-------------------------------------------|---|

|                                           |   |

|                                           |   |

|                                           |   |

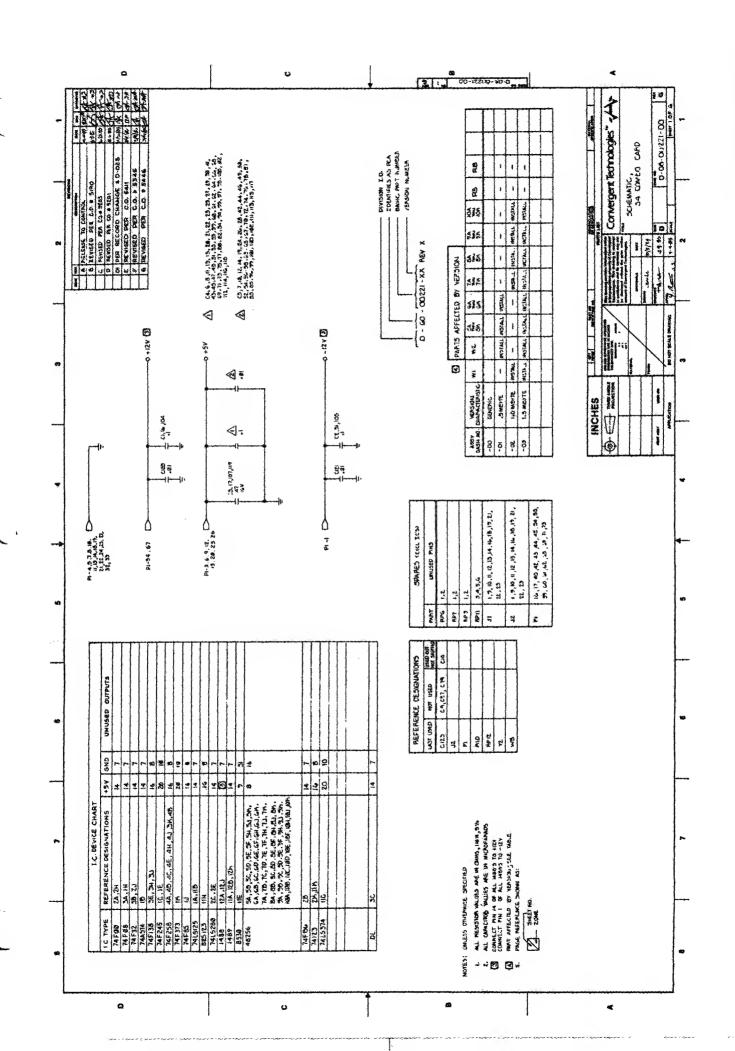

| Interface Circuitry Input/Output Handling | 1 |

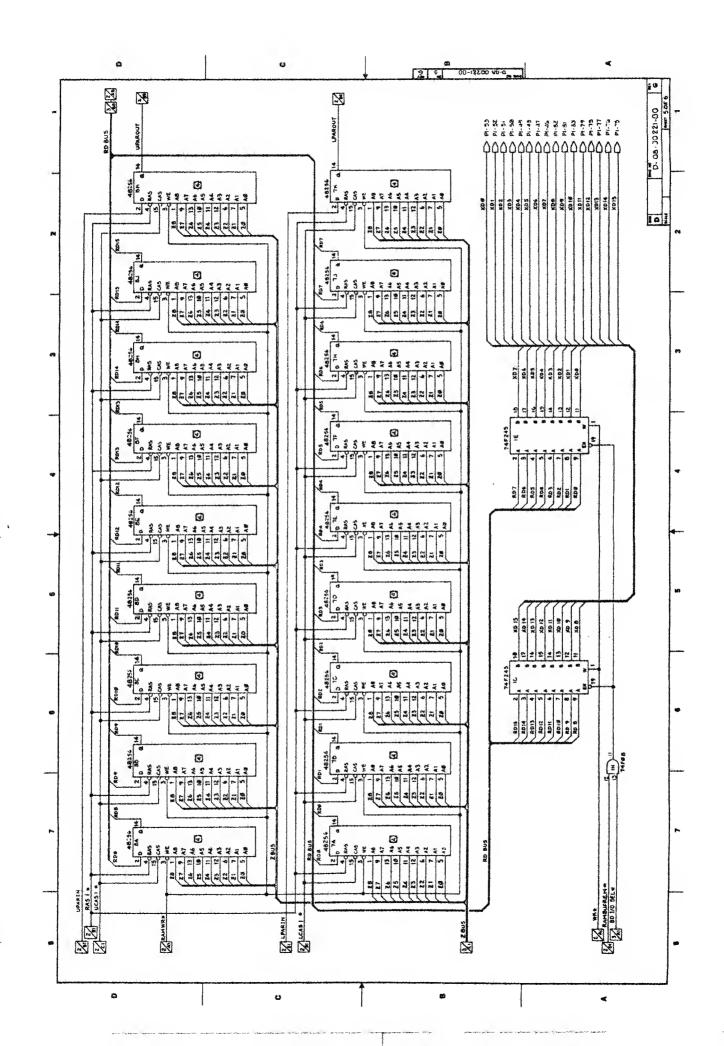

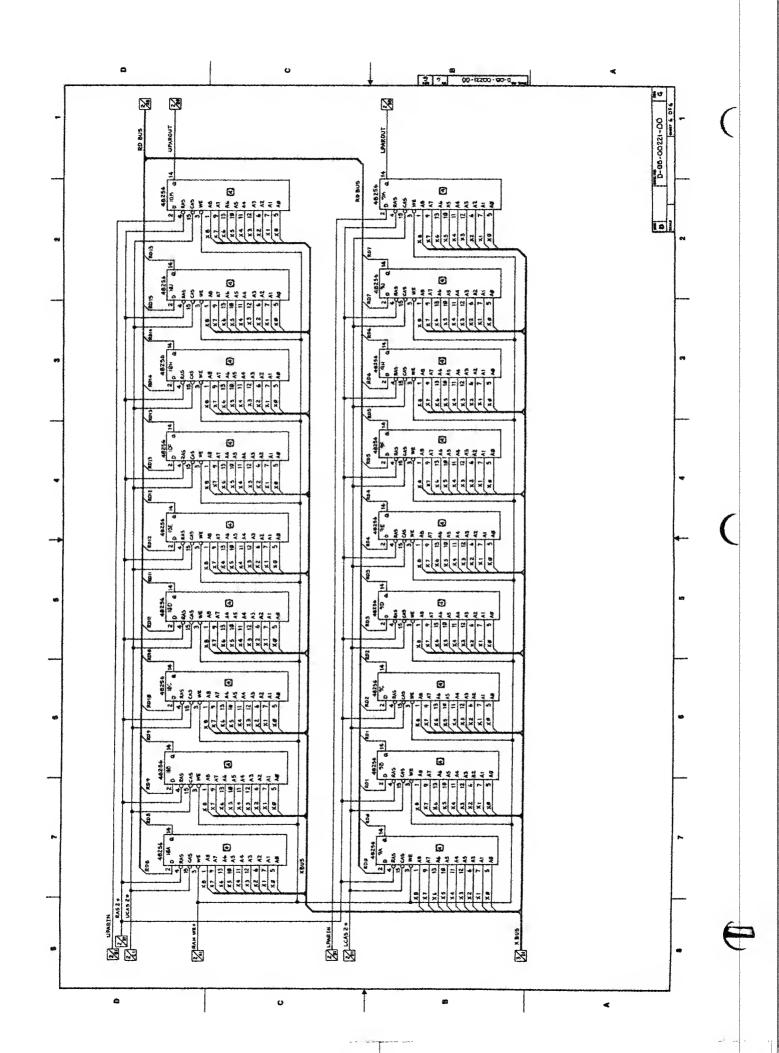

| Expansion Board Schematic                 | 2 |

The expansion hardware provides additional memory and communication capabilities for the AT&T UNIX PC. The expansion hardware's EIA ports make it possible for the PC to communicate with another terminal or computer. Additional memory and EIA capabilities are available separately or in combination, as shown in the following list of expansion hardware options:

- o 0.5MB RAM Expansion Board (no EIA ports)

- o 2.0MB RAM Expansion Board (no EIA ports)

- o 0.5MB EIA/RAM Combo Board (two EIA ports)

- o 1.0MB EIA/RAM Combo Board (two EIA ports)

- o 1.5MB EIA/RAM Combo Board (two EIA ports)

- o Dual EIA Port Board (no RAM, two EIA ports)

# The expansion hardware includes:

- o An interface connection P1 and associated circuitry

- o RAM memory

- o EIA connection circuitry (if an EIA or Combo board)

## Interface Circuitry

a Congradition !

All communications between the expansion board and the UNIX PC bus are through the expansion board interface connector P1.

### Input/Output Handling

As a direct memory access (DMA) device, data transfer from the expansion board to the PC bus causes the 68010 to wait while data is transferred into RAM memory. Data transfer is considered a fast cycle (500 ns).

There are three functions which the expansion board may be called upon to perform. Read to memory, read from memory and port to or from memory to the RS-232 interface.

## Expansion Board Schematic

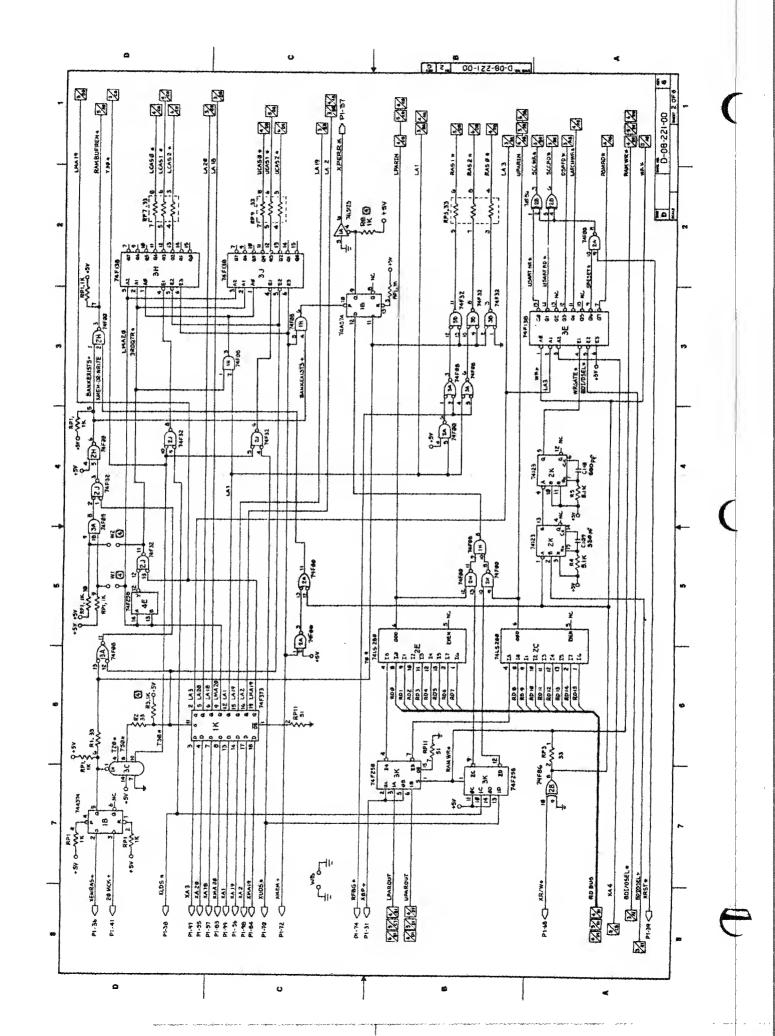

Sheet 2--Memory Access Control Circuitry:

This circuitry consists of address latch 1K, lower and upper data strobe control, consisting of demultiplexers 3H and 3J and OR gates 3B and parity interrupt, 2C and 2E.

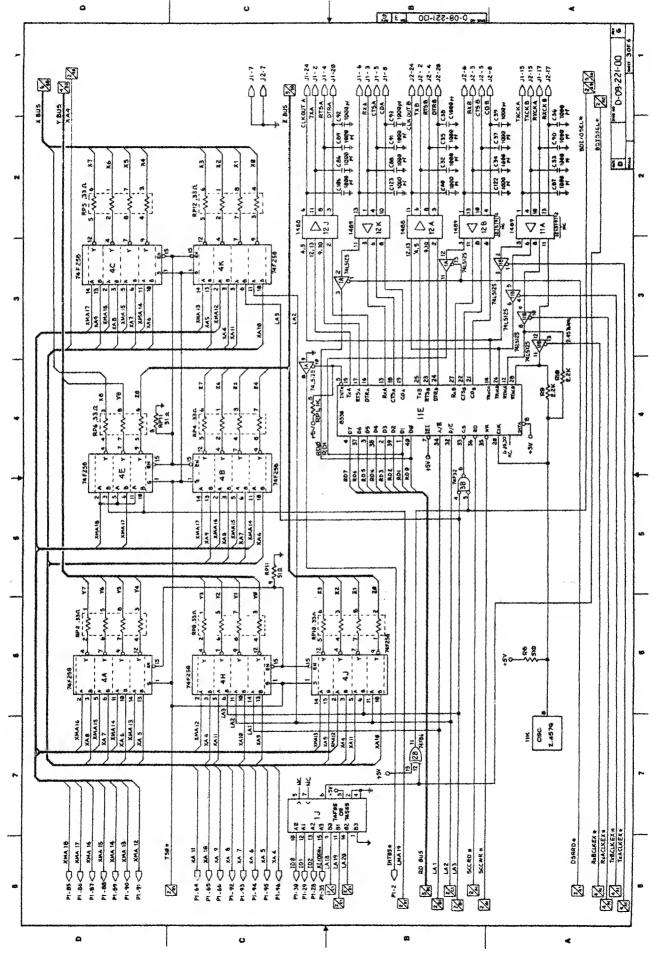

Sheet 3--Memory Bus Management and Communications Circuitry:

The upper portion of sheet 3 of the schematic contains map address management circuitry consisting of multiplexers 4A, 4B, 4C, 4E, 4H, and 4J. The lower portion of sheet 3 contains the communication interface IC 11E, RS-232 line drivers 12J, 12K, and 12A, and RS-232 receivers 11A and 12B and port connectors J1 and J2.

#### Note

This circuitry is present only on the EIA/RAM Combo and EIA/RAM boards. The 0.5 and 2.0 RAM expansion boards do not contain interface circuitry or RS-232 ports.

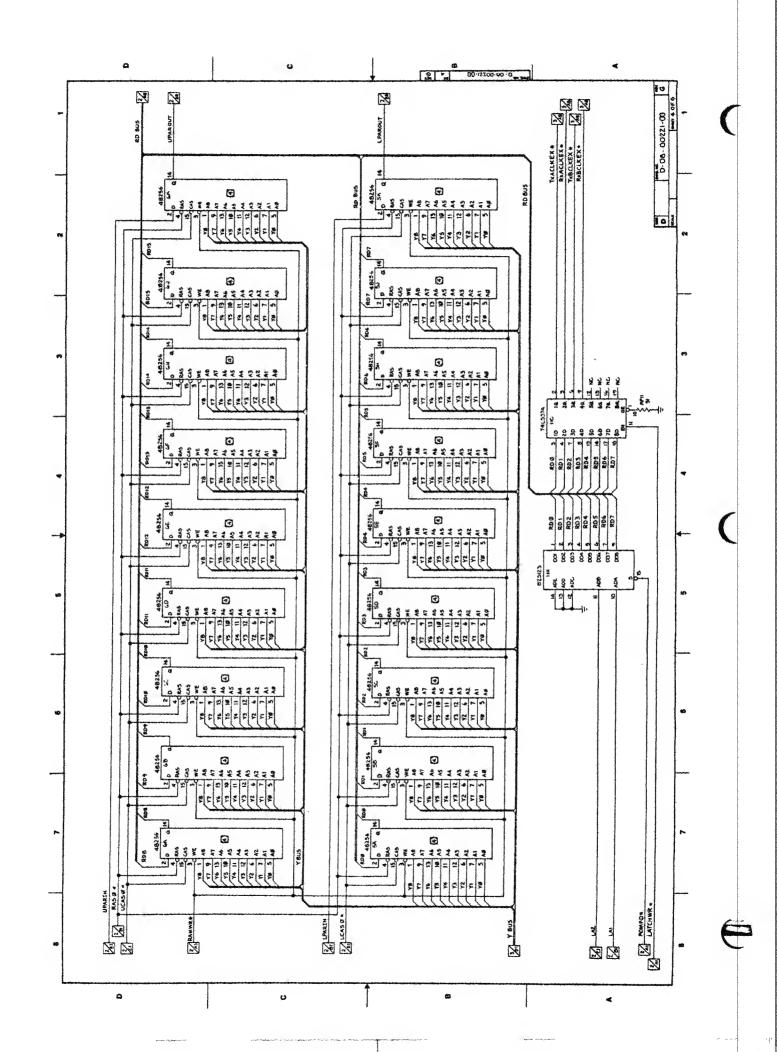

Sheets 4, 5 and 6--Memory (RAM):

Memory circuitry consists of the X, Y, and Z bus, the read bus and read bus control 11H and 11C, and upper and lower parity generator ICs 5K through 10K.

Depending on the amount of RAM that is mounted physically on the expansion board, these locations may or may not be used.

Sheet 5--Expansion Bus Interface:

The lower portion of sheet 5 of the schematic also contains data transceivers 1C and 1E connected to the read bus and expansion bus connector P1 completing the expansion loop.